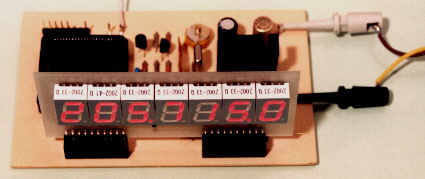

Im Dezember'2002 wurde von mir ein einfacher Frequenzzähler fertiggestellt, der komplett in einem programmierbaren Logikbaustein (CPLD) der Firma XILINX realisiert wurde.

Die max. Eingangsfrequenz beträgt ca. 200 MHz. Das verwendete CPLD ist mit 15ns Pin-to-Pin Laufzeit nicht gerade das schnellste. Umso größer war die Überraschung, dass der Zähler mit einer so hohen Frequenz (ohne Vorteiler) funktioniert.

Der Frequenzzähler hat folgende Eigenschaften:

|

-

|

7-stellige, gut ablesbare 7-Segment LED-Anzeige |

|

-

|

Auflösung 100 Hz, feste Torzeit 10 ms |

|

-

|

kompletter Zähler in einem CPLD realisiert |

|

-

|

extern nur ein Quarzoszillator und Treiber für die 7 Anzeigenstellen notwendig |

|

-

|

Betriebsspannung 7V ... 12V DC |

|

-

|

max. Stromaufnahme ca. 230 mA bei fx = 200 MHz |

|

-

|

CPLD auf der Platine programmierbar |

Schaltbild

(Anzeige als GIF-Bild im Browser)

Schaltbild (SPLAN Datei)

Layout

Zählerplatine (SPRINT-Layout Datei)

Layout Anzeigenplatine (SPRINT-Layout Datei)

Hardware-Design

Der gesamte Zähler wurde in der Hardware-Beschreibungssprache VHDL erstellt (Datei counter.vhd). Die Pin-Belegung und die Festlegung weiterer Parameter erfolgt im "User Constraints File" counter.ucf .

Mit diesen beiden Files und entsprechenden Tools aus dem Internet sowie einem einfachen Download-Kabel für den Parallel-Port des PC's kann jeder den Frequenzzähler in ein XC9572-CPLD programmieren (Infos s.u.).

Mit dem fertigen Programmier-File kann man sich das Compilieren und "Fitten" sparen:

Weiterführende Links

Wer sich für VHDL interessiert und den Einstieg in diese Hardware-Programmiersprache sucht, der sollte mal hier reinschauen : VHDL Beispiele und Links

Falls sich jemand entschließt, den Frequenzzähler nachzubauen oder falls jemand Tipps zum Programmieren von Xilinx-CPLD's sucht (Compiler/Fitter, Download-Kabel usw.) - hier gibt es einige Informationen dazu : CPLD-Tools zur Programmierung

Leiterplatten für eine leicht modifizierte Variante, programmierte CPLDs und unbearbeitete Gehäuse gibt es bei DF1TY, siehe Links.